# Waveform Characterization and Modeling of Dynamic Charge Behavior of InGaP-GaAs HBTs

C.-J. Wei, S. Sprinkle, J.T. Hu\*, H.-C. Chung, B. Mitchell, P. Dicarlo and D. Bartle

Alpha Industries Inc. 20 Sylvan Road, Woburn, MA 01801

\*Network Device Inc. 1230 Bordeaux Dr. Sunnyvale, CA 94089

**Abstract** — This study presents a novel time-domain characterization method for the first time, to reveal dynamic charge behavior of HBTs. The charge model plays an important role for power InGaP-GaAs HBT amplifiers designed with self-biasing. It is shown that charge-storage and extraction from the base of the HBT at a high-power drive can not be described by conventional quasi-static model. A new collector-base charge model is proposed to account for the time-response of the devices.

## I. INTRODUCTION

Power amplifiers for advanced wireless handsets are required to have single polarity bias, high efficiency and low distortion. HBTs have proven to be a competitive candidate. To predict the power performance, dc and bias-dependent S-parameters, it requires an accurate HBT model, including charge model.

During the last few years, a number of HBT models have been proposed with emphasis on self-heating effects [1][2][3][4][5]. Some of them also take into account the non-quasi-static charge [4][5]. Trans-capacitance of base-collector has been shown to have higher-order effects on HBT performance, namely linearity and distortion. Otherwise, there is no clear-cut evidence of its effects on transient response and power performance. A GP HBT model combined with self-heating modeling is sufficient to fit dc as well as small-signal response at various forward operation biases. However, it is found that this classic model fails to generate accurate large-signal time response at a high power drive, especially when there is a self-biasing resistor in the base bias circuit. Self-biasing is widely utilized in power amplifiers to enhance stability, help to eliminate thermal corruption.

Time-domain characterization has been recognized as a valuable tool for modeling of transistors and diodes [6][8]. The time response can be used to reveal non-quasi-static effects of devices, for instance, in a step-recovery diode. In this paper we present a method of waveform characterization as a supplemental extraction approach to the conventional bias-dependent S-parameter approach, to de-embed the non-quasi-charge behavior.

## II. DYNAMICAL CHARGING REVEALED BY WAVEFORMS

Waveform measurement technique has been presented elsewhere (4). The system was vector-calibrated with 50 ohm terminated. The fundamental was 0.9 GHz and 8 harmonics were measured. The transistors used in this work were GaInP/GaAs HBTs of four unit cells, each of 240  $\mu\text{m}^2$  emitter area with two emitter fingers of 3 $\mu\text{m}$  by 40 $\mu\text{m}$  and a ballast resistor of 40 ohm on the base. The input power is from 11 to 13 dBm and quiescent collector current was 70 mA at  $V_{\text{C}}=3.2$  V. The driving power is sufficient to swing the collector voltage to saturation region where both junction are partially conductive.

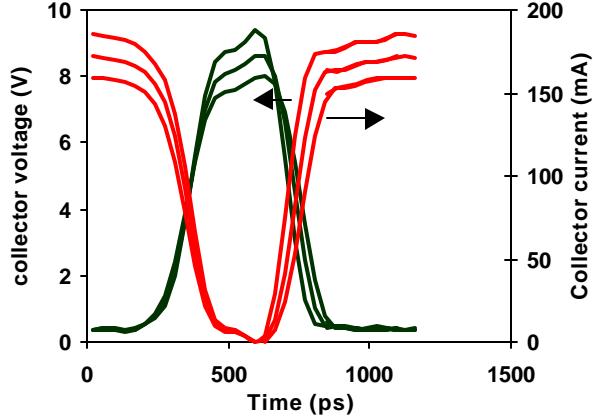

Figure 1. Collector voltage and collector current waveform of a 960  $\mu\text{m}^2$  HBT.  $V_{\text{C}}=3.2$  V,  $V_{\text{beo}}=1.28$  V and  $P_{\text{in}}=11, 12$  and 13 dBm.

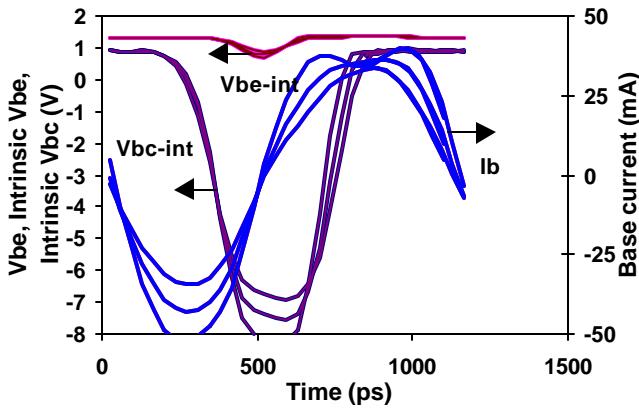

Fig.1 shows the collector voltage and collector current waveforms. Given that the parasitic resistances and inductances are de-embedded as described in section III. The intrinsic base-emitter voltage  $V_{\text{bei}}$  and intrinsic base-collector voltage  $V_{\text{bci}}$  can be calculated as shown in Figure 2, in that the base current is also plotted. It is shown that the  $V_{\text{bei}}$  is clamped around at  $V_{\text{bei}}=1.3$  V where the base-emitter junction is at forward, as expected. The  $V_{\text{bci}}$ , however, is clamped at around or less than 1.0V,

far below the collector-base built-in voltage, 1.23 V measured from DC. The base current, as shown in fig. 2, swings from positive to negative during the time period where the  $V_{bci}$  or  $V_{bei}$  is kept clamped. The time response of current is a resemblance of that of microwave step-recovery diode under RF drive. When the RF current swings to negative, the junction is kept at forward until all the charges stored at junction is extracted out. Obviously, the quasi-charge model is not applicable here. A good description of non-quasi-static charging effects is assuming an infinite or a very high capacitance at clamped voltage. The infinite capacitance model is valid for an ideal case of non-charge consumption in the base, neither by recombination nor by extraction of opposite junction field.

Figure 2. Intrinsic base-emitter voltage and intrinsic base-collector current waveforms of a 960  $\mu\text{m}^2$  HBT.  $V_{co}=3.2\text{V}$ ,  $V_{be0}=1.28\text{V}$  and  $P_{in}=11, 12$  and 13 dBm

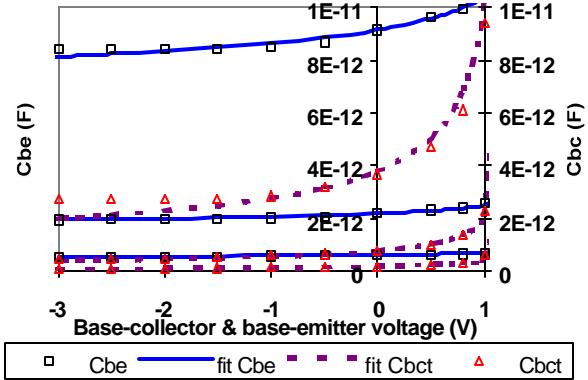

Figure 3. Measured (symbol) and fitted (line) base-collector and base-emitter capacitance vs. base voltage for 240, 960 and 3840  $\mu\text{m}^2$  devices, respectively from top down.

A very high capacitance at  $V_{bc}$  of about 1V is, however, contradictory to the measured values from S-parameters, as shown in figure 3, where no extraordinarily high capacitance at  $V_{bc}=1\text{V}$  can be seen. In order to be

consistent with small-signal models at various biases, we assume that the base-collector charge storage at saturation region is also a function of base-emitter voltage. A forward BE-junction creates charge storage at the BC junction due to an enhanced emitter barrier. At  $V_{bci}=1\text{V}$  the field of collector space-charge-region becomes too small to drift the charges to the collector, leaving the base charges waiting for extraction at a reverse base current. Thus the effective turn-on voltage for charging becomes 1 V instead of 1.23V.

### III. HBT MODEL EXTRACTION AND MODIFICATION

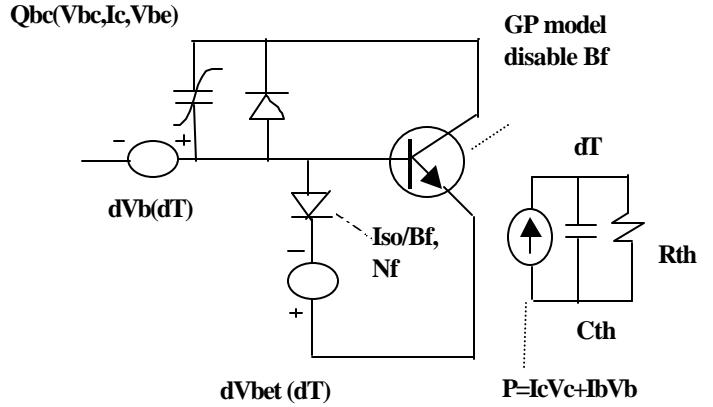

To extract large-signal model of HBTs, dc, thermal and S-parameter characterization have been utilized. Conventional Gummel-Poon model in conjunction with self-heating circuit is found sufficient to fit  $I_c$ - $V_c$  and  $V_{be}$ - $V_c$  curves. The self-heating effects are modeled by a thermal-subcircuit and two nonlinear feed-back circuits, as shown in fig.4, one used to model the decrease of  $V_{bi}$  of junctions with temperature, the other models the decreases of current gain. The capacitance-voltage dependencies of both junctions are extracted at  $V_{be}<1.2\text{V}$  and  $V_{bc}<1.0\text{V}$  or cut-off conditions, as shown in figure 3. The forward and collector transit time as function of  $V_{cb}$  and  $I_c$  is extracted from S-parameters at forward biases. The extraction approach of charge-related parameters and parasitic resistances and inductances are described previously [7].

Figure 4. Schematic of intrinsic HBT model consisting of a GP HBT model, thermal circuit, two feedback sources and modified BC charge

It is found that the model generated is adequate to be able to fit the S-parameters at both forward and reverse operation regions. There are some problem to fit S-parameters at saturation region. Inclusion of transcapacitance associated with current and transit time, as described in (5), was made to help to fit the measured results at high current region. It turns out, however, that it is difficult to accurately de-embed the junction

capacitance at heavy forward bias because of the shunting by the junction conductance.

To account for the apparent clamping of  $V_{bei}$  at lower voltage, we introduce a modified collector charge term  $Q_c(V_{bceff})+I_c \tau_c$ , where  $Q_c$  is the original charge model as function of  $V_{bc}$ , and  $V_{bceff} = V_{bc} + V_{be}$ . The collector capacitance then can be expressed as

$$C_{bc}(V_{bc}, V_{be}) = C_{bco}(I_c) / (1 - (V_{bc} + V_{be})/V_{bi})^m \quad (4)$$

$$C_{bc}(V_{bc}, V_{be}) = C_{bco}(I_c) / (1 - f_c)^m (1 - f_c(1+m) + mV_{bc}/V_{bi}) \quad (5)$$

Where

$$V_{be} = g(1 + \tanh(f(V_{be} - U))) \quad (6)$$

and  $g$ ,  $f$  and  $U$  are the fitting parameters.  $U$  is somewhere below the B-E building voltage. Essentially, a forward base-emitter voltage modifies the B-C build-in voltage by  $V_{be}$  and the modified value becomes zero when  $V_{be}$  drops to below  $U-1/f$ . Here  $f_c$  is assumed close to 1, to say 0.98. Therefore, the  $C_{bc}$  becomes very high when  $V_{bc}$  is equal to 1.23V- $V_{be}$ .

Apparently, the modification does not significantly affect the base-collector capacitance characteristics at reverse active region where the emitter junction is at cutoff. The change of collector charge at forward operation region is a minor factor because the capacitance varies with  $V_{bc}$  insignificantly for a negative bias. Thus the modification occurs mostly at saturation region.

#### IV. EXTRACTION AND MODELING RESULTS

In addition to  $240 \text{ um}^2$ ,  $960 \text{ um}^2$  and  $3840 \text{ um}^2$  are also measured for scalability study. The transistor was ballasted for thermal stability. The thermal resistance  $R_{th}$  is measured and fitted by a formula,  $R_{th} = 46639x(Ac)^{-0.7463}$ . Self-heating effect on built-in voltage is modeled by  $\delta V = -0.0012 * \delta T * \exp(\delta T/T_0)$  and its effect on current gain is expressed by a nonlinear term  $\delta \beta = -0.014 * \delta T / (T_0 * n_f * V_t) * \exp(\delta T/T_0)$ . The dc and parasitic related parameters for unit cell are:

(b)

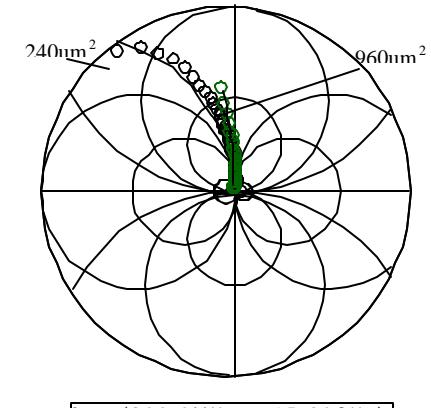

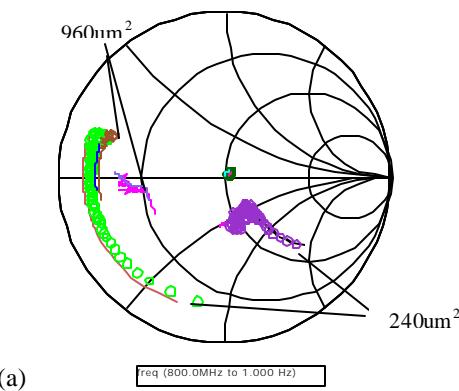

Figure 5. Model (line) vs measured (symbol) for S11, S12, S22 (a) and for S21 (b), respectively. Both  $240$  and  $960 \text{ um}^2$  are plotted in the same figure.  $V_c = 3 \text{ V}$ ,  $I_c = 13 \text{ mA}$  per  $240 \text{ um}^2$ .

$I_{so} = 1.52 \text{ e-24}$ ,  $N_f = N_r = 1.008$ ,  $B_f = 133.0$ ,  $I_{se} = 1.53 \text{ e-22}$ ,  $N_e = 1.285$ ,  $I_{sc} = 1.2 \text{ e-14}$ ,  $N_c = 1.88$ ,  $B_r = 0.4$ ,  $x_{jc} = 0.63$ ,  $R_e = 0.353$ ,  $R_{bi} = 0.55$ ,  $R_{bx} = 1.046$  and  $R_c = 1.144$ .

The charge related parameters are:

$C_{jc} = 0.205 \text{ pF}$ ,  $V_{jc} = 1.23$ ,  $m_c = 0.55$ ,  $C_{je} = 0.523 \text{ pF}$ ,  $V_{je} = 1.4$ ,  $m_e = 0.08$ ,  $T_{fo} = 8 \text{ ps}$ ,  $x_{tf} = 0.7$ ,  $v_{tf} = -5$ ,  $I_{tf} = 0.13 \text{ A}$  and  $T_r = 50 \text{ ps}$ .

The parameters associated with charge modification are:  $g = 1.2$ ,  $U = 1.18$ , and  $f = 4$ .

It is found that the model is scalable up to  $3840 \text{ um}^2$  in terms of reproducing dc and s-parameters at various biases. The fitting error is within 5% for both  $V_{be}$  vs  $V_c$  and  $I_c$  vs  $V_c$  curve families. Figure 5a and 5b, shows respectively the comparison of modeled s11, s12, s22, and s21, respectively, for a  $240 \text{ um}^2$  unit cell and  $960 \text{ um}^2$  devices using a unified scalable large-signal model. To be scalable, the scaling rule for extrinsic resistances and inductances are experimentally determined and fitted by nonlinear expressions.

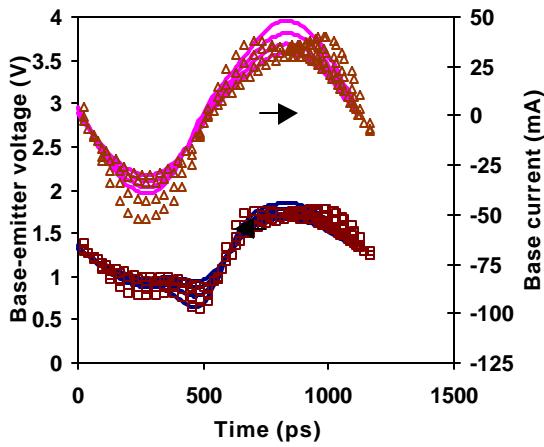

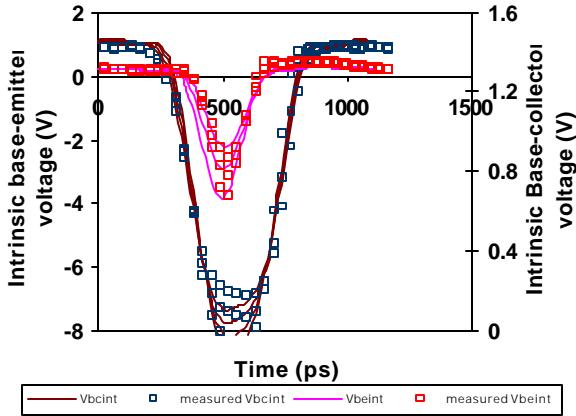

In order to validate the proposed model for large-signal response, the simulated time response of the device at a 50ohm-termination condition is compared to the measured. Figure 6 and 7, respectively, shows the simulated versus measured time response of  $V_b(t)$  and  $I_b(t)$ , and waveforms of intrinsic  $V_{be}(t)$  and intrinsic  $V_{bc}(t)$ . It is shown indeed that the intrinsic  $V_{bc}$  clamped at about 1V and the waveforms compare to the measured very well.

Figure 6. Modeled (line) vs measured (symbol) base voltage and base current waveforms.  $F=0.9\text{GHz}$ ,  $V_c=3.2\text{V}$ ,  $V_{bo}=1.28\text{V}$ ,  $P_{in}=11, 12$  and  $13\text{dBm}$ .

Figure 7. Modeled (line) vs measured (symbol) intrinsic B-E voltage, BC voltage.  $F=0.9\text{GHz}$ ,  $V_c=3.2\text{V}$ ,  $V_{bo}=1.28\text{V}$ ,  $P_{in}=11, 12$  and  $13\text{dBm}$ .

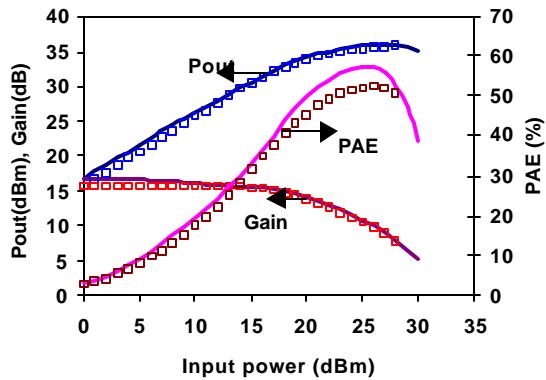

Figure 8. Simulated (line) vs measured (symbol) power performance of last stage of a GSM amplifier,  $V_c=3.2\text{V}$ ,  $I_{co}=0.4\text{A}$ .

The model was further verified in simulation of a real GSM power amplifier. The last stage of power amplifier is a  $7840\text{ um}^2$  device with an input capacitance tuning and a self-bias resistance. Figure 8 plots the simulated vs measured output power, power-added efficiency and power gain as functions of input power. The power output is limited by the self-biasing because of the negative move of the base bias voltage. Classic model generates more serious self-biasing than measured and it wrongly predicts  $1.2\text{ dBm}$  lower power but  $15\%$  higher PAE. Owing to the dynamic charge injection and extraction in the new model, less charge storage is resulted on the external capacitance, leading to higher power output.

## V. CONCLUSION

Time-domain measurements have revealed the dynamic charge or non-quasi charge behavior of InGaP-GaAs HBTs. A new charge model is present to account for the dynamic charging effects. In addition to excellent fitting to the dc, S-parameters, the model successfully predicts the time response and power performance for power amplifier, which, therefore, validated the model. The model is accurate, temperature-dependent and scaleable and it can be used for wireless power amplifiers where self-biasing and large-sized devices are employed.

## REFERENCES

- [1] R. Anholt, "Electrical and Thermal Characterization of MESFETs, HEMTs, and HBTs," Artech House, Boston, 1995

- [2] K. Lu, T. J. Brazil, "A New Spice-Type HBT Model for DC, Microwave Small-Signal Circuit Simulations," *1994 IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 3, pp. 1579-1582, June 1994.

- [3] Q.M. Zhang, J.Hu, J.Sitch, R.K. Surridge and J.M. Xu, "A New Large Signal HBT Model", *1994 IEEE MTT-S Digest*, pp.1253-1256.

- [4] J.Ph. Fraysse, D. Floriot, Ph. Auxemery, M. Campoccchio, R. Quere and J. Obregon, "A Non-quasi-Static Model of GaInP/AlGaAs HBT for Power Applications," *1997 IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 2, pp. 379-382, June 1997.

- [5] C.-J. Wei, J.C.M. Hwang, W.J. Ho, and J.A. Higgins, "Large-Signal Modeling of Self-Heating, Collector Transit-time, and RF-Breakdown Effects in Power HBTs," *IEEE Trans. Microwave Theory and Tech.*, vol. MTT-44, no. 12, pp. 2641-2647, December 1996.

- [6] C.-J. Wei, Y.A. Tkachenko, and D. Bartle, "Waveform Measurement Technique and Its Applications to Optimum Loading Studies on Power FETs," in digest of *2000 ICMMT*, Beijing, pp. 666-669, September, 2000

- [7] C.-J. Wei and J.C.M. Hwang, "New Method for Direct Extraction of HBT Equivalent Circuit Parameters," *IEEE Trans. Microwave Theory and Tech.*, vol. MTT-43, no. 6, pp. 896-904, June 1996.

- [8] C.-J. Wei, Y.E. Lan, and J.C.M. Hwang, "Waveform-Based Modeling and Characterization of Microwave Power Heterojunction Bipolar Transistors," *IEEE Trans. Microwave*

*Theory and Tech.*, vol. MTT-43, no. 12, pp. 2809-2903, June 1995.